## Table of content

| ESREF 2015 Editorial                                             | 3  |

|------------------------------------------------------------------|----|

| ESREF 2015 Committees                                            | 4  |

| Steering Committee                                               | 4  |

| Organizing Committee                                             | 5  |

| Technical Program Committee                                      | 6  |

| Event Committee                                                  |    |

| ESREF 2015 Invited Papers                                        | 11 |

| Keynote talks                                                    | 11 |

| Sister conference exchange papers                                |    |

| Invited papers in topical sessions                               | 13 |

| ESREF 2015 Tutorials                                             | 19 |

| ESREF 2015 Workshops                                             | 25 |

| Chip level Advanced Failure Analysis case studies                |    |

| Student Research Speed Dating                                    |    |

| Modeling the reliability at system level : tools and methodology |    |

| Advanced tools and techniques flash presentations                |    |

| Methods and tools for Failure Analysis and Reliability           |    |

| Fault isolation - defect localization                            | 27 |

| Sample Prep                                                      | 27 |

| Non Destructive Testing and Physical Characterization            |    |

| Nanoscale electrical measurement                                 |    |

| OEMs for components providers                                    |    |

| DSM Technology impact on safety assessment                       |    |

| Failure Analysis of Critical Systems                             |    |

| European FIB Users Group workshop                                |    |

| Reliability of avionics power electronics                        |    |

| Design and test for robustness and reliability                   |    |

| Design for reliability (PCB, subsystem level)                    |    |

| Statistical Analysis of Big Test Data                            |    |

| Radiation testing on electronic devices                          |    |

| ESREF 2015 program                                               |    |

| Monday, October 5, 2015                                          |    |

| Tuesday, October 6, 2015                                         |    |

| Wednesday, October 7, 2015                                                                | 43 |

|-------------------------------------------------------------------------------------------|----|

| Thursday, October 8, 2015                                                                 | 49 |

| Friday, October 9, 2015                                                                   | 54 |

| ESREF 2015 Paper Abstracts                                                                | 56 |

| SESSION A: Quality and Reliability Assessment - Techniques and Methods for Device Systems |    |

| SESSION B1: Si-Technologies & Nanoelectronics: Hot carriers, high K, gate materials       | 59 |

| SESSION B3: Si-Technologies & Nanoelectronics: ESD, Latch-up, Radiation Effects           | 61 |

| SESSION C: Failure Analysis                                                               | 63 |

| SESSION D1: Microwave & Power Wide Band-Gap SC Devices                                    | 66 |

| SESSION D2: Photonic                                                                      | 68 |

| SESSION D3: Photovoltaic & Organic Devices                                                | 70 |

| SESSION E1: Packaging & Assembly                                                          | 71 |

| SESSION E2: MEMS, MOEMS, NEMS & Nano-objects                                              | 73 |

| SESSION F: Power devices                                                                  | 74 |

| SESSION G: Space, Aeronautic & Embedded Systems                                           |    |

| SESSION H: European FIB User Group (EFUG)                                                 | 80 |

| ESREF 2015 Build your own ESREF 2015                                                      | 81 |

| ESREF 2015 Lab Tours                                                                      | 82 |

| LAAS Lab tour                                                                             | 82 |

| ITEC-Lab                                                                                  | 82 |

| TRAD Industry tour                                                                        | 84 |

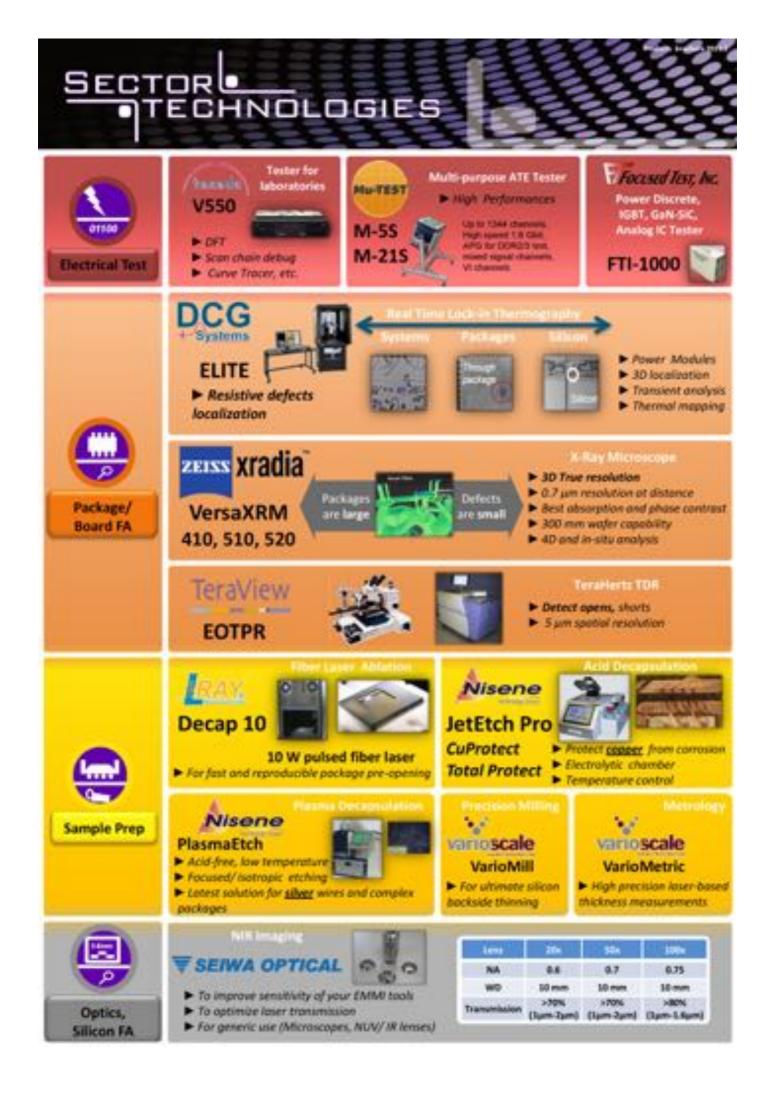

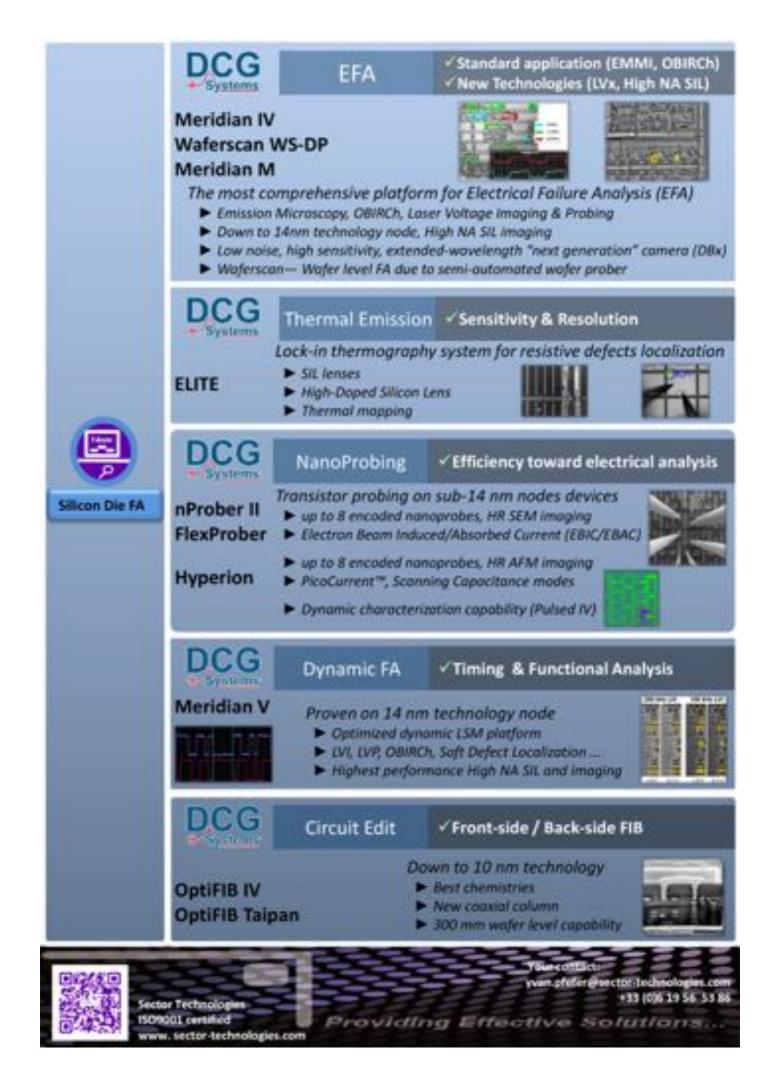

| ESREF 2015 Industrial Sponsors                                                            | 85 |

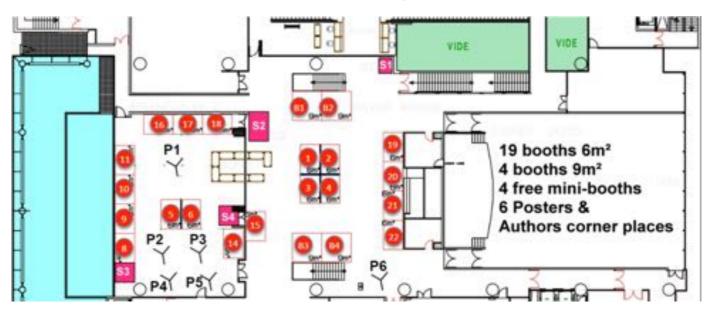

| ESREF 2015 Exhibition                                                                     | 88 |

| ESREF 2015 Exhibiting Companies description                                               | 88 |

| Exhibition layout                                                                         | 96 |

| ESREF 2015 Practical Information                                                          | 97 |

| Toulouse, the Pink City                                                                   | 97 |

| Public transportation                                                                     | 97 |

| Mobile application                                                                        | 97 |

## ESREF 2015 Editorial

Welcome to the 26<sup>th</sup> European Symposium on Reliability of Electron Devices, Failure Physics and Analysis, ESREF 2015, at Toulouse (France) from October 5<sup>th</sup> to October 9<sup>th</sup>, 2015.

This international symposium continues to focus on recent developments and future directions in Quality and Reliability Management of materials, devices and circuits for micro-, nano-, and optoelectronics. It provides a European forum for developing all aspects of reliability management and innovative analysis techniques for present and future electronic applications.

For its first time in Toulouse - world center for aeronautics with Airbus assembly line, European capital of the space industry and number 1 in France for embedded electronic systems - specific topics are dedicated to these applications involving severe environment and harsh reliability challenges in addition to the core topics of the conference.

The Technical Program of ESREF 2015 has been defined by the Technical Program Committee (TPC) organized in thirteen sub-committees with more than 250 renowned experts in the field of reliability of electronic components and systems. The TPC has proceeded to a careful selection from 252 extended summaries and selected 103 papers to be presented during the oral sessions and 62 as posters. This conference would not be possible without the commitment and expertise of all these contributors.

Our main focus in 2015 is space, aeronautics and embedded systems. Two keynote speeches – one related to Mars exploration reliability challenges and the other on hardware cybersecurity – will open the conference on Monday, October 5. Over the three next days, the conference is organized in four parallel topical tracks composed of tutorials, invited presentation, session and workshop. Nine invited speakers who are recognized experts in their fields will give an overview of the state-of-the-art and special focus on advanced research work.

Within the topical tracks, 8 tutorials are offered to allow attendees refreshing and expanding their knowledge.

Based on an exchange agreement with the committees of the International Symposium on the Physical & Failure Analysis of Integrated Circuits Conference (IPFA 2015), the International Reliability Physics Symposium (IRPS 2015) and the International Symposium for Testing and Failure Analysis (ISTFA 2014), authors of awarded papers have been invited to present their work at ESREF 2015. These exchanges prove the fruitful collaboration between the Committees of these three conferences.

10 Workshops organized in correlation with the ESREF conference will give the opportunity to exchange the knowhow and field returns on specific topics and in particular, in relationship with aeronautics, space and embedded systems.

Exhibition with state-of-the-art equipment starts on Monday afternoon and will host coffee breaks, lunches, poster sessions and author's corner to maximize interaction between attendees and exhibitors.

Finally, we would like to warmly thank all our sponsors that allowed setting up this exciting and high-quality program:

the IEEE Electron Devices Society for its technical co-sponsorship.

the Centre National de la Recherche Scientifique (CNRS),

the University of Toulouse III - Paul Sabatier,

the Centre National d'Etudes Spatiales (CNES)

SO Toulouse Convention Bureau

and our industrial sponsors:

Gold sponsor: Sector Technologies

Silver sponsors: THALES Group and Hamamatsu,

Bronze sponsors: Digit Concept, FEI, Intraspec Technologies, Kleindiek nanotechnik, Orsay Physics, Raith GmbH.

All the members of the Program and of the Technical Committees, all the reviewers and the Corresponding Members deserve our congratulations and our thanks for their involvement and their efforts to make ESREF meet the requirements of an international event dedicated to Quality and Reliability of Electron Devices.

We are very happy to meet you in TOULOUSE for a memorable experience.

Marise BAFLEUR

ESREF 2015 Chair

Terde

Philippe PERDU ESREF 2015 Vice-Chair

## **Steering Committee**

Alain BENSOUSSAN Jaap BISSCHOP Christian BOIT Giovanni BUSATTO Mauro CIAPPA Yves DANTO Ingrid De WOLF Gert ERIKSEN Fausto FANTINI **Bruno FOUCHER** Philippe GALY Wolfgang GERLING Siegfried GOERLICH **Ralf HEIDERHOFF** Nathalie LABAT Jim R. LLOYD Gaudenzio MENEGHESSO **Enrique MIRANDA** Jean-Luc MURARO George PAPAIOANNOU Philippe PERDU Cora SALM Ninoslav STOJADINOVIC André TOUBOUL Massimo VANZI Eckhard WOLFGANG Wolfgang WONDRAK

IRT Saint Exupéry / Thales Alenia Space(France) NXP Semiconductors (The Netherlands) TUB - Tech. University of Berlin (Germany) University of Cassino (Italy) ETH Zürich (Switzerland) IMS, University of Bordeaux (France) IMEC (Belgium) GRUNDFOS (Denmark) University of Modena (Italy) AIRBUS GROUP INNOVATION (France) STMicroelectronics (France) ECPE (Germany) Infineon (Germany) University of Wuppertal (Germany) IMS, University of Bordeaux (France) University of Albany (USA) University of Padova (Italy) University Autonoma Barcelona (Spain) THALES Alenia Space (France) University of Athens (Greece) CNES (France) University of Twente (The Netherlands) University of Nis (Serbia) IMS, University of Bordeaux (France) University of Cagliari (Italy) ECPE (Germany) Daimler Chrysler (Germany)

### **Organizing Committee**

LAAS-CNRS (France)

TU Berlin (Germany)

NEOCERA (USA)

LAAS-CNRS (France)

EMPA (Switzerland)

Freescale (France)

University of Modena (Italy)

University of Cassino (Italy)

ETH Zürich (Switzerland)

Intraspec Technologies (France)

Fraunhofer-Institute for Mechanics of Materials (Germany)

IMS, University of Bordeaux (France) IMS, University of Bordeaux (France)

CNES (France)

**Conference Chair & Vice-Chair** Marise BAFLEUR Philippe PERDU

**Technical Program Chairs** Hélène FREMONT François MARC

**Conference Scientific Support** Christian BOIT Fausto FANTINI

Industrial Exhibition Jan GAUDESTAD Brigitte DUCROCQ

Tutorial chair Peter JACOB Giovanni BUSATTO

Workshop chairs Mauro CIAPPA Thomas ZIRILLI Fulvio INFANTE

Best Paper Award chair Matthias PETZOLD

Best Poster Award chair David TRÉMOUILLES

LAAS-CNRS (France)

Audio/Video chairs Nicolas MAURAN Nicolas NOLHIER

Organization Secretariat Ascension DE SOUSA BERDAT

Event Committee chairs Alain BENSOUSSAN André DURIER

Publicity Chairs Jérome TOUZEL Enrique MIRANDA LAAS-CNRS (France) LAAS-CNRS (France)

LAAS-CNRS (France)

IRT Saint-Exupéry (France) IRT Saint-Exupéry (France)

INFINEON (Germany) University Autonoma Barcelona (Spain)

**Microelectronics Reliability Journal Edition Chairs**

Marise BAFLEUR Philippe PERDU Nicolas NOLHIER Hélène FREMONT François MARC Edition Chairs LAAS-CNRS (France) CNES (France) LAAS-CNRS (France) IMS, University of Bordeaux (France) IMS, University of Bordeaux (France)

ESREF Scientific support in TURKEY Ilknur BAYLAKOĞLU

SATURN Consulting (Turkey)

Webmaster David TRÉMOUILLES

LAAS-CNRS (France)

### **Technical Program Committee**

Chairs: Hélène FREMONT, IMS, University Bordeaux (France) – François MARC, IMS, University Bordeaux (France)

Quality and Reliability Assessment - Chairs: Ninoslav D. STOJADINOVIC, University of Nis (Serbia) - Bruno FOUCHER, AIRBUS GROUP INNOVATIONS (France) Christelle AUPETIT-BERTHELEMOT, ENSIL Florian MOLIERE, Airbus Group Innovations (France) University of Limoges (France) Lirida NAVINER, TELECOM ParisTech (France) Olivia BLUDER, Kompetenzzentrum für Automobil-Alexander NIKIFOROV, National Research Nuclear und Industrieelektronik GmbH - (Austria) University "MEPHI" (Russia) Yves DANTO, IMS, University of Bordeaux (France) Albena PASKALEVA, Bulgarian Academy of sciences Vojkan DAVIDOVIC, University of NIS (Serbia) (Bulgaria) Milan JEVTIC, Institute of Physics (Serbia) M.K. RADHAKRISHNAN, Nanorel (India) Dimitrios KOUVATSOS, Institute NCSR "Demokritos" Didier REGIS, THALES GROUP (France) (Greece) Cora SALM, MESA+ Research Institute/ University of Andreas MIDDENDORF, TU Berlin / Fraunhofer IZM Twente (The Netherlands) (Germany)

#### Si Technologies & Nanoelectronics: Hot carriers, high K, gate materials - Chairs: Alain BRAVAIX, ISEN (France) - Jim STATHIS, IBM Research (USA)

Xavier AYMERICH, Univ. Autonoma Barcelona (Spain) Jean COIGNUS, CEA-LETI (France) Rainer DUSCHL, Infineon Technologies (Germany) Gabriella GHIDINI, STMicroelectronics (France) Dimitrios KOUVATSOS, Institute NCSR "Demokritos" (Greece) Paolo PAVAN, Università di Modena e Reggio Emilia (Italy)

Nagarajan RAGHAVAN, Singapore University of Technology and Design (Singapore)

Rosana RODRIGUEZ, Universitat Autonoma de Barcelona (Spain)

Cora SALM, MESA+ Research Institute/ University of Twente (The Netherlands)

#### Si Technologies & Nanoelectronics: Low K, Cu Interconnects - Chairs: Hervé JAOUEN, STMicroelectronics (France) - Eckhard LANGER, Globalfoundries (USA)

Lucile ARNAUD, CEA Leti (France) Oliver AUBEL, Globalfoundries (Germany) Fen CHEN, IBM (USA) Cathryn J CHRISTIANSEN, IBM (USA) Kristof CROES, IMEC (Belgium) Vincent DWYER, Loughbourough University (UK) Xavier FEDERSPIEL, STMicroelectronics (France)

Martin GALL, Fraunhofer IKTS-MD (Germany) Chee Lip GAN, Nanyang Technological University (Singapore) Howard GAN, SMIC (China) Andrea PADOVANI, University of Modena (Italy) Xin-Ping QU, Fudan University (China) Frank SCHLAPHOF, Globalfoundries (Germany)

#### Si Technologies & Nanoelectronics: ESD, Latch-up, Radiation Effects - Chairs: Fabrice CAIGNET, LAAS-CNRS (France) - Philippe GALY, STMicroelectronics (France) - Vesselin VASSILEV, NOVORELL Technologies (USA)

Bruno ALLARD, AMPERE- INSA Lyon (France) Patrice BESSE, Freescale Semiconductor (France) Gianluca BOSELLI, Texas Instruments (USA) Lorenzo CERATI, STMicroelectronics (Italy) Denis FLANDRE, SST/EPL Ecole Polytechnique de Louvain (Belgium) Hörst GIESER, Fraunhofer IZM (Germany) Harald GOSSNER, Intel (Germany) Allesio GRIFFONI, OSRAM (Italy) Richard JANSEN, ESA (The Netherlands) Martin KERBER, Infineon (Germany) Paul LEROUX, KU Leuven (Belgium)

Martino LORENZINI, NXP (The Netherlands) Alessandro PACCAGNELLA, Università di Padova (Italy) Vincent POUGET, IES - Univ. Montpellier 2 (France) Mobile Christian RUSS. Intel Communications (Germany) Pascal SALOME, Serma Technologies (France) Adelina SHICKOVA, Infineon (Germany) Gerald SOELKNER, Infineon (Germany) Gerd VERMONT, ON Semiconductor (Belgium) Hei WONG, City University of Hong Kong (China) Beiping YANG, ASTRI (Hong Kong-China)

Failure Analysis – Chairs: Félix BEAUDOIN, GLOBALFOUNDRIES (USA) - Olivier CREPEL, AIRBUS GROUPINNOVATIONS (France) - Siegfried GOERLICH, INFINEON (Germany) - Ralf HEIDERHOFF, Bergische UniversitätWuppertal (Germany)Abdellatif FIRITI, NXP (The Netherlands)Koji NAKAMAE, IST Osaka (Japan)

Juergen GRUBER, ROOD MICROTEC (Germany) Stewart HOLLINGSHEAD, Texas Instruments (USA) Terence KANE, IBM (USA) Susane LI , SPANSION (USA) Ted LUNDQUIST, DCG Systems Wolfgang MERTIN, University Duisburg-Essen (Germany) Giovanna MURA, University of Cassino (Italy) Koji NAKAMAE, IST Osaka (Japan) Vincent POUGET, IES (France) Antoine REVERDY, Sector Technologies (France) Jean-Philippe ROUX, Sector Technologies (France) Kevin SANCHEZ, CNES (France) Christian SCHMIDT, GlobalFoundries (USA) Zhigang SONG, IBM (USA) Ehrenfried ZSCHECH, Fraunhofer IZFP (Germany)

**D1: Wide Band-Gap SC Devices** – Chairs: *Peter FRIEDRICHS*, INFINEON (D) - *Nathalie LABAT*, IMS, University Bordeaux (France) - *Gaudenzio MENEGHESSO*, University of Padova (Italy)

Andrew BARNES, ESA/ESTEC (The Netherlands) MALBERT, IMS, University Nathalie Bordeaux (France) Michael DAMMAN, IAF Fraunhofer IAF (Germany) Denis MARCON, IMEC (Belgium) Dan FLEETWOOD, Vanderbilt University (USA) Roberto MENOZZI, University of Modena (Italy) Tsuyoshi ISHIKAWA, Toyota Central R&D labs Jean-Luc MURARO, Thales Alenia Space (France) (Japan) Karine ISOIRD, LAAS-CNRS (France) Dionyz POGANY, TU WIEN (Austria) Benoit LAMBERT. United Monolithic Semiconductors Michael UREN, University of Bristol (UK) (France) Giovanni VERZELLESI, University of Modena (Italy) Toshiide KIKKAWA, Transphorm Japan (Japan) Joachim WÜRFL, Ferdinand-Braun-Institut Jan KUZMIK, Slovak Academy of Sciences (Slovakia) (Germany)

**D2: Photonic Devices** – Chairs: *Matteo MENEGHINI*, University of Padova (Italy) - *Massimo VANZI*, University of Cagliari (Italy)

| Christelle AUPETIT-BERTHELEMOT, ENSIL –               | Juan JIMENEZ, University of                |

|-------------------------------------------------------|--------------------------------------------|

| University of Limoges (France)                        | Robert KAPLAR, SANDIA NA                   |

| Laurent BECHOU, IMS University Bordeaux (France)      | Michel KRAKOWSKI, Thales                   |

| Alain BENSOUSSAN, IRT Saint-Exupéry (France)          | Laurent MENDIZABAL, CEA                    |

| Daniel CASSIDY, University of McMaster                | Giovanna MURA, Univ. Cagl                  |

| Yannick DESHAYES, IMS University of Bordeaux (France) | Tigran NSHANIAN, Philips L<br>Netherlands) |

| Alessio GRIFFONI, OSRAM (Italy)                       | Osamu UEDA, Kanazawa Ur                    |

Juan JIMENEZ, University of Valladolid (SP) Robert KAPLAR, SANDIA NATIONAL LABS (USA) Michel KRAKOWSKI, Thales 3-5 LAB (France) Laurent MENDIZABAL, CEA-LETI (France) Giovanna MURA, Univ. Cagliari (Italy) Tigran NSHANIAN, Philips Lumileds Lighting Co (The Netherlands) Osamu UEDA, Kanazawa University (Japan)

#### D3: Photovoltaic & Organic Devices – Chair: *Nicola WRACHIEN*, University of Padova (Italy)

Andrea CESTER, University of Padova (Italy) Cosimo GERARDI, ST Microelectronics (Italy) Ralf HEIDERHOFF, University of Wuppertal (Germany) Morten MADSEN, University Of Southern Denmark (Denmark) Laurent MENDIZABAL, CEA-LETI (France) Selina OLTHOF, Univ. Cologne (Germany) Andrea REALE, Università di Roma Tor Vergata (Italy) Thomas RIEDL, University of Wuppertal (Germany) Elisabeth VON HAUFF, Univ. Amsterdam (The Netherlands) E1: Packaging & Assembly – Chairs: *Geneviève DUCHAMP*, IMS, University Bordeaux (France) -*Kirsten WEIDE-ZAAGE*, University of Hannover (Germany)

Y. C CHAN, City University Hong Kong (China) Wilson MAIA, THALES R&T (France) Lorenzo CIANI, University of Florence (Italy) Lutz MEINSHAUSEN, Washington State University (USA) Alberto CORIGLIANO, Politecnico di Milano (Italy) Frédéric RICHARDEAU, LAPLACE-INPT (France) Paolo COVA, Università di Parma (Italy) René RONGEN, NXP (The Netherlands) Yves DANTO, IMS, University of Bordeaux (France) Vincent ROUGET, AIRBUS Group Innovations Christian GAUTIER, Presto Engineering (France) (France) Alexandrine GUEDON-GRACIA, IMS, University of Mohd Faizul bin Mohd SABRI, University of Malaya Bordeaux (France) (Malaysia) Xiao HU LIU, IBM TJ Watson Research Center (USA) Suhana Mohd SAID, University of Malaya (Malaysia) Fulvio INFANTE, Intraspec Technologies (France) Marc WURZ, IMPT, University of Hannover (Germany) Yong LIU, Fairchild Semiconductor (USA)

#### E2: MEMS, MOEMS, NEMS & Nano-objects - Chairs: Fabio COCCETTI, elemca (France) - George

**PAPAIOANNOU**, University of Athens (Greece) Elena BLOKHINA, University College Dublin (Ireland) Manuel DOMINGUEZ, Universitat Polytechnica Cataluna (Spain) David ELATA, Technion, Israel Institute of Technology (Israel)

Evgeni GOUSEV, Qualcom Technologies Inc (USA)

Loukas MICHALAS, IMM – CNR (Italy) Patrick PONS, LAAS-CNRS (France) Bruno REIG, LETI – CEA (France) Herbert SHEA, EPFL (Switzerland) Jun-Bo YOON, KAIST (Korea)

| <b>F : POWER DEVICES</b> – Chairs: <i>Patrick TOUNSI</i> , INSA, (Germany) | LAAS-CNRS (France) - <b>Eckhard WOLFGANG</b> , ECPE                                     |

|----------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|

| Stéphane AZZOPARDI, IMS, Univ. Bordeaux (France)                           | Thomas LICHT, University of Applied Sciences in                                         |

| Reinhold BAYERER, Infineon (Germany)                                       | Düsseldorf (Germany)                                                                    |

| Philippe BENECH, IMEP-INPG (France)                                        | Josef LUTZ, TU Chemnitz (Germany)                                                       |

| Frede BLAABJERG, Aalborg University (DK)                                   | Régine MALLWITZ, TU Braunschweig (Germany)                                              |

| Giovanni BREGLIO, University of Naples Federico II<br>(Italy)              | Michael NELHIEBEL, KAI Kompetenzzentrum<br>Automobil- und Industrieelektronik (Germany) |

| Giovanni BUSATTO, University of Cassino (Italy)                            | Ichiro OMURA, Kyushu Institute of Technology (Japan)                                    |

| Alberto CASTELLAZZI, University of Nottingham (UK)                         | Martin PFOST, Reutlingen University (Germany)                                           |

| Dinesh CHAMUND, Dynex Semiconductor (UK)                                   | Frédéric RICHARDEAU, LAPLACE-INPT (France)                                              |

| Mauro CIAPPA, ETH Zurich (Switzerland)                                     | Uwe SCHEUERMANN, SEMIKRON (Germany)                                                     |

| Chiara CORVASCE, ABB (Switzerland)                                         | Hans-Joachim SCHULZE, Infineon (Germany)                                                |

| Paolo COVA, University of Parma (Italy)                                    | Norbert SELIGER, Rosenheim University of Applied                                        |

| Adeline FEYBESSE, FREESCALE (USA)                                          | Sciences (Germany)                                                                      |

| Laurent GUILLOT, FREESCALE (France)                                        | Dieter SILBER, University of Bremen (Germany)                                           |

| Karsten GUTH, Infineon (Germany)                                           | Hiroshi SUZUKI, HITACHI (Japan)                                                         |

| Francesco IANUZZO, University of Cassino (Italy)                           | Peter TUERKES, Infineon (Germany)                                                       |

| Andrea IRACE, University of Naples Federico II (Italy)                     | Jean-Michel VINASSA, IMS, Univ. Bordeaux (France)                                       |

| Nando KAMINSKI, University of Bremen (Germany)                             | Wolfgang WONDRAK, Daimler (Germany)                                                     |

| Kai KRIEGEL, Siemens (Germany)                                             | Eric WOIRGARD, IMS, Univ. Bordeaux (France)                                             |

| Stephane LEVEBVRE, CNAM (France)                                           |                                                                                         |

|                                                                            |                                                                                         |

|                                                                            |                                                                                         |

**G:** Space, Aeronautic & Embedded Systems – Chairs: Sonia BEN DHIA, LAAS-CNRS (France) - André DURIER, IRT Saint-Exupéry (France) - Florent MILLER, AIRBUS GROUP INNOVATIONS (France) - Fabian VARGAS, Catholic University - PUCRS (Brazil)

Marcos Osmar AREND, AEL, Sistemas/Elbit Systems Ltd. (Brazil)

İlknur BAYLAKOĞLU, SATURN Consulting – (Turkey) Eduardo BEZERRA, Federal University of Santa Catarina, Florianópolis (Brazil)

Jerónimo BLOSTEIN, Centro Atómico - Instituo Balseiro, Bariloche (Argentina)

Leticia Maria BOLZANI POEHLS, Catholic University - PUCRS, Porto Alegre (Brazil)

Stéphanie BOURBOUSE, Airbus Defence and Space (France)

Véronique FERLET CAVROIS, ESA (The Netherlands) David HELY, Grenoble Institute of Technology (France)

Jean Claude LAPERCHE, Airbus Group (France)

Dominique LENOIR, Renault (France)

Fernanda LIMA KASTENSMIDT, Federal University of Rio Grande do Sul, Porto Alegre (Brazil)

José LIPOVETZKY, Centro Atómico - Instituo Balseiro, Bariloche (Argentina)

Renaud MANGERET, Airbus Defence and Space (France)

Francesca MARADEI, Sapienza de Rome (Italy)

Maria MAZUREK, Airbus Group (France)

Guy PEREZ, CNES (France)

Mohamed RAMDANI, ESEO (France)

Matteo SONZA REORDA, Politecnico di Torino, Torino (Italy)

Régine SUTRA ORUS, IRT Saint-Exupéry-Zodiac (France)

Daniel TRIAS, Serma Technologies (France)

Damien VERDIER, Continental (France)

Bertrand VRIGNON, Freescale Semiconductor (France)

H: European FIB User Group (EFUG) – Chairs: *Frank ALTMANN*, Fraunhofer IWM Halle (Germany) - *Hugo BENDER*, IMEC (Belgium) - *Hélène CHAUVIN*, Thales Group (France)

Martina DIENSTLEDER, FELMI, ZFE (Austria)

Christophe GUERIN, DGA (France)

Gareth HUGHES, University Oxford (UK)

Domenico MELLO, STMicroelectronics (Italy)

Moritz-Andreas MEYER, Globalfoundries (Germany)

Valery RAY, PBS&T, MEO Engineering (USA)

Thomas ZIRILLI, Freescale Semiconductor (France)

### **Event Committee**

#### Chairs: Alain BENSOUSSAN - IRT Saint Exupéry, André DURIER, IRT Saint Exupéry

This new committee, called Event committee, in majority composed of industrials, helped us with the organization of ESREF and suggested new ideas to improve the local attractivity of the conference.

.

...

| Members            |                          |  |  |

|--------------------|--------------------------|--|--|

| Philippe ARGUEL,   | LAAS-CNRS                |  |  |

| Marise BAFLEUR,    | LAAS-CNRS                |  |  |

| Laurent BECHOU,    | IMS-Bordeaux             |  |  |

| Bruno VIALLE,      | Fahrenheit Epsilon-Alcen |  |  |

| Philippe CABON,    | ACTIA                    |  |  |

| Xavier CHAUFFLEUR, | Fahrenheit Epsilon-Alcen |  |  |

| Olivier CREPEL,    | AIRBUS Group Innovation  |  |  |

| Brigitte DUCROCQ,  | LAAS-CNRS                |  |  |

| Jean-Marie DILHAC, | LAAS-CNRS                |  |  |

| Bertrand FORGERIT, | Hirex Engineering        |  |  |

| Bruno FOUCHER,     | AIRBUS Group Innovation  |  |  |

| Frédéric HOEPPE,   | Nexio                    |  |  |

| Fulvio INFANTE,    | Intraspec Technologies   |  |  |

| Philippe LASSERRE, | PRIMES-Innovation        |  |  |

| Benoit LEPINE,     | CEA Tech                 |  |  |

| David LOHIER,      | Hirex Engineering        |  |  |

| Jean-Luc MURARO,   | Thales Alenia Space      |  |  |

| Philippe PERDU,    | CNES                     |  |  |

| Pierre PETIT,      | Continental              |  |  |

| Yannick POIRE,     | Nexio                    |  |  |

| Philippe PONS,     | AIRBUS GROUP             |  |  |

| Alain RAMOND,      | Yzatec                   |  |  |

| Didier REGIS,      | Thales Group             |  |  |

| Sébastien SALAS,   | CAPTRONIC                |  |  |

| Christel SEGUIN,   | ONERA                    |  |  |

| Jérôme TOULZE,     | AIRBUS GROUP             |  |  |

| Alain WISLEZ,      | Thales C&S               |  |  |

| Thomas ZIRILLI,    | Freescale Semiconductor  |  |  |

## -CNRS -CNRS Bordeaux nheit Epsilon-Alcen ł nheit Epsilon-Alcen **JS Group Innovations** -CNRS -CNRS Engineering JS Group Innovations pec Technologies ES-Innovation **Tech** Engineering s Alenia Space nental JS GROUP С s Group RONIC RA **JS GROUP**

## Keynote talks

Monday October 5, 14:20, Cassiopee room

ChemCam instrument on the Curiosity rover: from R&D to operations on Mars; be reliable or die... Sylvestre MAURICE, IRAP, France

The ChemCam project started as an R&D program at CNES in 2001, was selected by NASA in 2005, launched in 2011, and is operated on the Curiosity rover at Mars since 2012. It consists of a high energy laser which creates, at distance, a plasma on Mars soils and rocks to infer their elemental composition. Quality and reliability

were inherent to the development of this very innovative instrument that has to work in a very unusual environment (Mars surface) at 350 million km distance, for the first time on "the most complex robot ever done by JPL", in the end to find out if Mars was in the past an habitable world. I'll trace back this unique experience with emphasis on Quality and Reliability management.

**Sylvestre MAURICE** is the Deputy Principal Investigator for ChemCam. Along with Principal Investigator Roger Wiens, he is responsible for the design, construction, testing, and delivery of the LIBS instrument. He has previously worked on several projects including Cassini at Saturn, Lunar Prospector orbiting the Moon, and Mars Odyssey that have prepared him for the challenge of building an instrument for Mars exploration.

#### Monday October 5, 16:20, Cassiopee room

### Towards Hardware Cyber security

Ramesh Karri, Polytechnic Institute of New York University, USA

Hardware security and trust is an important design objective similar to power, performance, reliability and testability. I will highlight why hardware security and trust are important objectives from the economics, security, and safety perspectives. Important messages from this talk include (i) understanding simple gotchas when traditional DFT, test, and validation techniques are used (scan

chains, JTAG, SoC test, assertion based validation), (ii) understand how traditional DFT, test and validation techniques can be used to improve hardware security and trust and finally (iii) understand "Design for Trust" approaches that can provide testability without compromising security and trust.

**Ramesh Karri** is a Professor of Electrical and Computer Engineering at Polytechnic School of Engineering, New York University. He has a Ph.D. in Computer Science and Engineering, from the University of California at San Diego. His research interests include trustworthy ICs and processors; High assurance nanoscale IC architectures and systems; VLSI Design and Test; Interaction between security and reliability. He has over 150 journal and conference publications in these areas. These include two tutorial articles in IEEE Computer and three tutorial articles in Proceedings of IEEE on Trustworthy Hardware. He was the recipient of the Humboldt Fellowship and the National Science Foundation CAREER Award. He is the area director for cyber security of the NY State Center for Advanced Telecommunications Technologies at NYU-Poly; Hardware security lead of the Center for research in interdisciplinary studies in security and privacy -CRISSP (http://crissp.poly.edu/), co-founder of the Trust-Hub (http://trust-hub.org/) and organizes the blue NYU, Embedded annual red team team event at the Systems Challenge (http://www.poly.edu/csaw2014/csaw-embedded). He cofounded the IEEE/ACM Symposium on Nanoscale Architectures (NANOARCH). He is the Program Chair (2012) and General Chair (2013) of IEEE Symposium on Hardware Oriented Security and Trust (HOST). He is the Program Co-Chair (2012) and General Co-Chair (2013) of IEEE Symposium on Defect and Fault Tolerant Nano VLSI Systems. He is the General Chair of the 2009 and 2013 NANOARCH. He is the general co-chair of ICCD 2015, RFIDSEC 2015 and WISEC 2015. He serves on several program committees. He was the Associate Editor of IEEE Transactions on Information Forensics and Security (2010-2014), IEEE Transactions on CAD (2014-present), ACM Journal of Emerging Computing Technologies (2007- present), ACM Transactions on Design Automation of Electronic Systems (2014-present), IEEE Access (2015-present), IEEE Transactions on Emerging Technologies in Computing (2015-present) and IEEE Design and Test (2015-present). He is an IEEE Computer Society Distinguished Visitor (2013-present). He is on the Executive Committee of IEEE/ACM Design Automation Conference leading the Security@DAC initiative (2014-.) He has organized/delivered invited tutorials on Hardware Security and Trust (VLSI Test Symposium 2012, 2014, International Conference on Computer Design 2012, IEEE North Atlantic Test Workshop 2013, Design Automation and Test in Europe 2013, IEEE International Test Conference 2014, IEEE/ACM Design Automation Conference 2014, and IEEE International Test Conference 2014, and IEEE LATW 2014).

### Sister conference exchange papers

Monday October 5, 17:20, Cassiopee room

#### ISTFA 2014 Outstanding paper

Localization of Weak Points in Thin Dielectric Layers By Electron Beam Absorbed Current (EBAC) Imaging

**Jörg Jatzkowski, Michél Simon-Najasek and Frank Altmann**, Center for Applied Microstructure Diagnostics (CAM), Fraunhofer Institute for Mechanics of Materials, Halle, Germany

A novel approach for the localization of weak points in thin transistor and capacitor oxides before electrical breakdown will be presented in this paper. The proposed approach utilizes Electron Beam Absorbed Current (EBAC) imaging based on Scanning Electron Microscopy (SEM). This technique uses the generation of additional charge carriers within the semiconductor substrate level by scanning with a focused electron beam. Over a thin transistor or capacitor oxide layer inside the interaction volume of the electron beam an increased tunnel current is visualized by EBAC and areas with different current intensities indicating weak points become visible. These soft defect areas are investigated in comparison to references which were analyzed by using cross sectioning in a dual beam FIB/SEM system followed by a high resolution Transmission Electron Microscopy (TEM) investigation. The feasibility of this new technique is demonstrated on a defective transistor gate oxide test structure.

**Michél Simon-Najasek** received his diploma in electrical engineering at the University of Applied Science in Koethen / Germany in 2002. For more than 12 years he has been working in the research group "Diagnostic of semiconductor technologies" at Fraunhofer IWM / CAM in Halle, Germany. Michel's research field is failure analysis on Si and III/V based electronic devices mainly for automotive applications. He is expert in focused ion beam preparation, electron microscopy analysis and nanoprobing for IC level diagnostics. Michel is coordinating the failure analysis team within his research group.

Monday October 5, 17:45, Cassiopee room

#### IPFA 2015 Best paper

UTB GeOI 6T SRAM Cell and Sense Amplifier considering BTI Reliability

Vita Pi-Ho Hu, Pin Su, and Ching-Te Chuang, Department of Electronics Engineering & Institute of Electronics, National Chiao Tung University, Taiwan The impacts of NBTI and PBTI on the stability of UTB GeOI 6T SRAM cell and performance of sense amplifier compared with the SOI counterparts have been investigated. Worst case stress scenarios for read and write operations are analyzed. For UTB GeOI SRAMs, PBTI dominates the degradations in read static noise margin (RSNM), while for UTB SOI SRAMs, NBTI dominates the degradations in RSNM. Write static noise margin (WSNM) only slightly degrades due to NBTI and PBTI. Current latch sense amplifier (CLSA) and voltage latch sense amplifier (VLSA) are analyzed considering NBTI/PBTI for GeOI and SOI devices. GeOI CLSA and VLSA show smaller word-line to SAE buffer delay and sense amplifier sensing delay than the SOI counterparts.

**Vita Pi-Ho Hu** received the B. S. degree in department of Materials Science and Engineering and the Ph. D. degree in department of Electronics Engineering & Institute of Electronics from National Chiao Tung University, Hsinchu, Taiwan in 2004 and 2011, respectively. Her research interests include Silicon and IIIV-based nanoelectronics, ultra-low voltage/power SRAM and logic circuits using emerging devices, and device circuit interaction and co-optimization. From 2011 to 2015, she was an Assistant Research Fellow with National Chiao Tung University. She joins National Central University, Taoyuan, Taiwan as an Assistant Professor in Aug. 2015.

Monday October 5, 18:10, Cassiopee room

**IRPS 2015 Best paper**

#### Platform Qualification Methodology: Face Recognition

**Ghadeer Antanius, Rutvi Trivedi and Robert Kwasnick**, Intel Corporation, USA

Platforms may be developed with a range of new features. We describe a

methodology to qualify a platform for operational stability and functional reliability. This includes determining feature-specific goals and use conditions to achieve the desired user experience quality and reliability. We present detailed results for a client PC face recognition feature.

**Ghadeer Antanius** is an Engineering Manager at Intel Corporation. He is responsible for managing Intel Client Platforms Quality & Reliability including Notebooks, Tablets, Smart Phones and High End Desk Tops. He also manages the Platforms and New Technologies Quality & Reliability Goals and Use Conditions across all Intel market segments. Mr. Antanius holds an Electrical Engineering bachelor's degree. He has two issued US patents.

### Invited papers in topical sessions

Tuesday October 6, 8:00, Spot room

#### Invited paper Session Session C: Failure Analysis

#### EOBT: from past to future

Ludwig BALK, University of Wuppertal, Germany

It is now fifty years ago that both electron beams and laser sources became commercially available to enable inspection techniques for all kinds of applications, but in special for the characterization and the testing of electronics devices. This happened more or less simultaneously with the beginning of integration of electronic

components. While at the early times a simple imaging was done only, in the mid 60ies first work was carried out using all kinds of interaction products due to the impact of optical and electron beams to determine device features and their malfunctioning. Those interaction products could well be particles or

photons as well as properties like electrical current and voltage. Although these kinds of testing techniques became more and more important, it took more than twenty year that a special conference on this topic was born: the 1st European Conference on Electron and Optical Beam Testing of Electronic devices (EOBT), which was organized in the year 1987 in Grenoble by Bernard Courtois and Eckhard Wolfgang. From then on this conference continued till 1995 as an independent meeting that had attracted several hundreds of scientists and engineers. However, as quite often in research, if a new field becomes mature, the size of a conference reduces, which gave rise to the decision of merging the EOBT with ESREF due to their strong overlap in the field of failure analysis. The EOBT remained an important topic, sometimes as a special session or in other years merged with failure analysis in general. Over the years it had turned out that simple systems cannot always fulfill the tasks needed, due to the reduced sizes of structures and the demand on extreme spatial resolution as well as due to the more and more complicated vertical structure of devices, making it necessary to either prepare devices destructively or to go for sources with high vertical penetration such as for instance ion beams. And last not least so-called hybrid systems came into being enabling the simultaneous measurement of various device properties. The presentation will give a review of some of the important advantages presented in all of the EOBT conferences, without being complete, and it will try to give a view into what may be the needs for future developments.

Professor Dr. Dr.h.c. **Ludwig Josef Balk** studied semiconductor physics at the RWTH Aachen and received his doctoral degree from the faculty of electrical engineering of the same university. After that he joined the department of materials for electrical engineering at the University of Duisburg. In 1991 he became full professor for electronics at the University of Wuppertal, where he was for many years dean of the faculty as well as executive director of the Institute of Polymer Technology. He got several awards, such as various visiting professorships and best papers at conferences. Further he was member of various scientific boards, the most prominent being member of the editorial board of Journal of Physics D for nearly twenty years. His scientific output consists of about 270 publications, out of these 55 invited or keynote papers, over 120 seminars in industry and academic, and 7 international patents.

Tuesday October 6, 11:00, Guillaumet room Invited paper Session E1: Packages & Assembly

#### Electromigration, still a reality for 3D ICs ?

#### Stéphane MOREAU, CEA-LETI, France

3D integration is booming, however, like any new integration/product, before being put on the market, it is necessary to check its reliability. This presentation focuses on the electromigration phenomenon, a degradation of metal levels, which could lead to

open circuits or possibly a short circuit, in the interconnections of future products (3DIC) integrating the 3-D approach. First, we address the problem in the case of an intra-chip interconnect, high density TSV-last (O3  $\mu$ m × 15  $\mu$ m) and then, in a second time, for inter-chip interconnect, Cu/SiO2 hybrid bonding. For these two case studies, the traditional main theme of a reliability study will be followed: test structures, tests, statistical analysis and failure analysis (fault location, morphological analysis, in situ SEM). The presentation will conclude on the problem of modeling the electromigration phenomenon.

**Stéphane Moreau** received his PhD in Electronics from Francois-Rabelais University (Tours, France) in 2005 on the environmental reliability of TRIAC (semiconductor switch), work done with STMicroelectronics (Tours, France). In 2006, he joined CEA-LETI (Grenoble, France) first as a postdoctoral fellow and then, in 2008, as a research engineer. His research areas include multiphysics simulations and reliability issues, especially electromigration and environment- induced damage (CTE mismatch, humidity...) for 3-D integration. He has authored or co-authored of more than 30 papers on those topics and served on the IRPS conference as reviewer.

#### Tuesday October 6, 13:40, Argos room

#### **Invited paper Session D2: Photonic Devices**

## A unified multiple stress reliability model for microelectronic devices – Application to 1.55 µm DFB laser diode module for space validation

Alain BENSOUSSAN et al, IRT Saint-Exupéry (F), Permanent address: Thales Alenia Space, France

The establishment of European suppliers for DFB Laser Modules at 1.55 µm is considered to be essential in the context of future European space programs, where availability, cost and schedule are of primary concerns. Also, in order to minimize the risk, associated with such a development, the supplier will be requested to use components, which have already been evaluated and/or validated and/or qualified for space applications. The Arrhenius model is an empirical equation able to model temperature acceleration failure modes and failure mechanisms. The Eyring model is a general representation of Arrhenius equation, which take into account additional stresses than temperature. The present paper suggests to take advantage of these existing theories and derives a unified multiple stress reliability model for electronic devices in order to quantify and predict their reliability figures when operating under multiple stress in harsh environment as for Aerospace, Space, Nuclear, Submarine, Transport or Ground. Application to DFB laser diode module technologies is analyzed and discussed based on evaluation test program under implementation.

**Alain Bensoussan** is engineer in Applied Physics from Institut National des Sciences Appliquees (INSA), Lyon (France), in 1979 and Doctor Engineer from INSA Toulouse (France) in 1984. He has been 7 years with the Centre National de la Recherche Scientifique (CNRS) at L.A.A.S. (Laboratoire d'Analyse et d'Architecture des Systemes) to complete his "These d'Etat" working on design and development of laser diode devices. Since 1987, he joined Thales Alenia Space, as now Senior Engineer with 32 years expertise in EEE parts including Microwaves, MEMS and Optoelectronic devices. He represented Thales Alenia Space at EUROSPACE organization, nominated by the "Eurospace" organization to support the Space Components User interests at ESA - PSWG (European Space Agency - Parts Policy and Standards Working Group) since more than 15 years. He is now, full time seconded at Institut de Recherche Saint Exupery, (Aeronautic, Space and Embedded Systems - AESE), Toulouse (France).

#### Wednesday October 7, 9:40, Guillaumet room

#### **Invited paper Session D2: Photonic Devices**

Failure analysis of photonic devices by high-resolution cathodoluminescence

#### David GACHET, Attolight AG, Switzerland

Quantitative cathodoluminescence (CL) microscopy is a new optical spectroscopy technique that measures optical characteristics over large fields of view with unprecedented spatial resolution without the need for tedious alignment. It is based on the careful intrication of an optical microscope and a custom designed scanning electron microscope (SEM). Thanks to the sensitivity of CL to material composition, as well as to the presence of defect, it is well suited for device characterization at sub micron scale. Here we present a selection of failure analyses and ageing effect studies performed with quantitative CL on optoelectronic devices.

**David Gachet** got a PhD in physics from the University of Aix-Marseille, France (2007) working on novel non-invasive contrasts in optical microscopy for biology. He then worked two years and a half (2008-2010) as a postdoctoral researcher at Weizmann Institute of Science (Rehovot, Israel) and Fresnel Institute (Marseille, France) in the field of optical spectroscopy and microscopy of nanoparticles. In 2010, he was appointed Assistant professor at the University of Aix-Marseille (France). Since 2013, he has been leading the Analytical laboratory of the Swiss company Attolight. The laboratory specializes in defect metrology and failure analysis in semiconductor devices using quantitative cathodoluminescence microspectrometry.

#### Wednesday October 7, 11:00, Argos room

## Invited paper Session B3: Si Technologies & Nanoelectronics: ESD, Latch-up, Radiation Effects

## Impacts of plasma process-induced damage on MOSFET parameter variability and reliability

#### Koji ERIGUCHI, Univ. of Kyoto, Japan

Plasma process-induced damage (PID) is one of critical issues in designing MOSFETs with higher performance and reliability, because PID is believed to enhance the reliability degradation and variability. In this study, damage creation mechanisms during plasma

processing — plasma-induced physical damage (PPD) and charging damage (PCD) — are focused on, and the impacts on MOSFET reliability are discussed. In PPD mechanisms, damaged structures result in threshold voltage (*V*th) shift and drain current decrease of MOSFETs, which are induced by Si recess (Si loss) in the source/drain extension region and the latent defects beneath the damaged region, respectively. The PPD also enhances the MOSFET parameter variability in LSIs due to plasma fluctuation. Model predictions of parameter variability in scaled FinFETs are presented on the basis of the PPD range theory and molecular dynamics simulations, where both stochastic straggling and sputtering play key roles. As for PCD, MOSFETs with high-k dielectrics are shown to suffer from "*V*thinstability" due to characteristic charge trapping. As a consequence, conflicting results among reliability data such as time-dependent dielectric breakdown (TDDB) lifetime are found under a certain amount of PCD, leading to erroneous conclusions in reliability assignments. Since these mechanisms are unscalable and intrinsic natures of plasma processing, the present PID models should be intensively implemented to design future LSIs with higher performance and reliability.

**Koji Eriguchi** received the B.S. and M.S. degrees in engineering physics and mechanics from Kyoto University, Japan, in 1989 and 1991, respectively, and the Ph.D. degree in engineering physics from Kyoto University in 2004. He has been an associate professor of Kyoto University since 2005, working on plasma–solid surface interaction, thin dielectric reliability degradation by plasma processing, optical characterization techniques of Si surfaces, and modeling of plasma-induced damage and defect creation in crystalline Si. Prior to joining Kyoto University, he had been a senior engineer at Panasonic from 1991, responsible for the research of plasma etch processes, thin gate dielectric wear-out phenomena including plasma-induced damage (PID), CMOS process integration, and reliability of CMOS devices. He has published more than 80 journal papers and 130 conference papers. He received the Best Paper Award from the 32nd Dry Process Symposium in 2009, the APEX/JJAP Paper Award and the Plasma-Electronics Award from the Japan Society of Applied Physics (JSAP) in 2010.

#### Wednesday October 7, 14:20, Guillaumet room

## Invited paper Session D1: Microwave and Power Wide Bandgap Devices

## Reliability Studies of Vertical GaN Devices Based on Bulk GaN Substrates

#### Isik KIZILYALLI, AVOGY - USA

There is a great interest in wide-bandgap semiconductor devices and most recently in vertical GaN structures for power electronics applications. In this paper, vertical p-n diodes and field-effect transistors fabricated on pseudo-bulk low defect density (104–106 cm–2) GaN substrates are discussed. Homo-

epitaxial low-pressure metal organic chemical vapor deposition growth of GaN on its native substrate and being able to control and balance the n-type Si doping with background C impurity has allowed the realization of vertical device architectures with drift layer thicknesses of 6 to 40  $\mu$ m and net carrier electron concentrations of 4 × 1015 to 2.5 × 1016 cm-3. This parameter range is suitable for applications requiring breakdown voltages (BVs) of 600 V-4 kV (and higher) with a proper edge termination strategy. Measured p-n diodes demonstrate near power device figure of merit, that is, differential specific on-resistance (Rsp) of

$2 \text{ m}\Omega$ -cm2 for a BV of 2.6 kV and 2.95 m $\Omega$ -cm2 for a 3.7-kV device, respectively. While, vertical transistors with BV=1500V and Rsp of 2.2 m $\Omega$ -cm2 have been fabricated. The improvement in the substrate quality over the last few years has resulted in the fabrication of diodes with areas as large as 16 mm2, with BVs exceeding 700 V and pulsed (100 µs) currents of 400 A. The structures fabricated are utilized to study in detail the temperature dependence of I–V characteristics, impact ionization based avalanche characteristics and ruggedness, reliability under high-temperature reverse bias, high-temperature operating life, temperature cycling, and temperature-humidity-bias test.

**Isik C. Kizilyalli** received the B.S., M.S. and Ph.D. (1982, 1984, and 1988) degrees from the University of Illinois in Urbana. His career since spans fundamental research in semiconductors to technology development, commercialization of innovation, and entrepreneurship. Currently, he is the Founder of Avogy Inc. (San Jose, CA) a venture backed start-up concerned with GaN power electronics and power systems. Previously he was with Bell Laboratories, followed by Nitronex Corporation, and solar PV startup Alta Devices where his group holds the world record for single junction solar cell conversion efficiency. Dr. Kizilyalli was elected a Fellow of the IEEE in 2007 and received the Bell Laboratories' Distinguished Member of Technical Staff award, in recognition for his contributions to CMOS transistor design.

#### Thursday October 8, 8:00, Cassiopee room

#### **Invited paper Session F: Power Devices**

## Destruction Failure Analysis and International Reliability Test Standard for Power Devices

#### Takashi SETOYA, Toshiba Corp, Japan

As for the demand for semiconductor power device, it is predicted these are growing drastically in future for EV/HEV and Natural energy connections. The power devices

are affected by the stress unlike the normal semiconductor device including a big electric current, the sudden temperature change, and it is an important problem how to guarantee the reliability. Therefore For power device, special evaluation methods and confirmation method are necessary. On the other hand, the trend such as publishing power semiconductor qualification guideline for vehicle is coming out of Japan. In this presentation are shown reliability test method, destruction measures, screening method, and failure analysis techniques for semiconductor power devices. Furthermore, this presentation is introducing an international standard trend of power devices.

**Takashi Setoya** is Chief Quality Executive of TOSHIBA Corporation Semiconductor & Storage Products Company, responsible for Reliability and Quality of discrete, Logic, analog, memory, SSD and HDD products. He joined TOSHIBA in1983. He is working for the quality and reliability of semiconductor more than 30years. He holds a bachelor's degree from HOSEI University, and He is a chairman of JEITA semiconductor technology reliability Committee, and a director of RCJ(Reliability center of Japan). He is married and has three children.

#### Thursday October 8, 9:20, Spot room

#### **Invited paper Session H: EFUG**

## Plasma FIB development for 3D IC structures investigations and X-ray tomography sample preparation"

#### Guillaume AUDOIT, CEA-LETI, France

To continue the increases in speed and density of microelectronic systems described by Moore (More Moore), 3D integration seems to be the next revolution in the IC industry. One major challenge of these architectures, which basically consist in stacking vertically different components, is the manufacturing and the associated

reliability and monitoring of the interconnections in between the components. The ability to physically characterize the interconnections such as through silicon vias (TSV) used in 3D integration is essential for developing robust manufacturing processes and fabricating reliable products. Focused ion beam (FIB) systems have long provided both physical analysis (FIB/SEM) and sample preparation such as TEM

lamellae, but conventional FIB cannot remove material fast enough to analyze the relatively large 3DIC structures. The high milling rate of the Plasma FIB technology has been developed to address these needs. We present here some developments for high rate ion induced metal deposition using a co-axial needle as a gas injection system and also beam parameters optimization for large milling of curtain free cross sections (example of a TSV). Furthermore, we present how the plasma FIB can be used as a very efficient way of preparing samples for X-ray tomography to investigate large 3D structures.

**Guillaume Audoit** obtained his engineer degree (M.S.) from the national school of chemistry in Montpellier in 2002 and a PhD in nanoscience in 2005 from the University College Cork. He spent 4 years in the industry working in physico-chemical characterization by FIB/SEM and TEM of a wide variety of inorganic materials. In 2010, he joined the nano- characterization platform of CEATech/Leti on Minatec campus Grenoble (France) to work on the sample preparation by focused ion beam for Transmission Electron Microscopy, Atom Probe Tomography, Secondary Ion Mass Spectrometry and Atomic Force Microscopy. He is now in charge of the sample preparation group, including more general preparation approaches such as mechanical polishing, accurate cleaving and dicing, chemical attack and broad beam ion milling. Its main fields of interest and experience include silicon-based microelectronics, 3DIC, sensitive materials preparation (GaAs, InP, GaN, etc...) and materials for new energies.

#### Thursday October 5, 15:20, Argos room

## Invited paper Session A: Quality and Reliability Assessment – Techniques and Methods for Devices and Systems

## Modelling the impact of refinishing processes on COTS components for use in aerospace applications

Christopher Bailey, University of Greenwich (GB)

This presentation will focus on predictive reliability of commercial off the shelf (COTS) components for high reliability applications in the aerospace and defence sectors. Reliability assessment of newly designed electronic products before their actual manufacture is a critical issue for many organisations. For example, products manufactured by the aerospace industry operate in extreme in- service environments and require very high reliability qualification (e.g. 25-30 years). The limited

availability of MiL-Spec components is forcing a number of high reliability markets, to consider the use of COTS electronic components. Many of the COTS components including BGA and QFN packages have not been designed for such high reliability applications. Therefore, characterizing and modelling the behaviour of these components and assessing their reliability and lifetime is a very important task. This presentation details the issues faced by organisations adopting COTS components such as Tin Whiskers and approaches adopted to mitigate these failures. Examples will be provided on the methodologies used to model and predict the reliability of these components and printed circuit boards for aerospace applications and how modelling can help optimise the ruggedisation, reliability and robustness of these components and printed circuit boards.

**Christopher Bailey** is the Professor of Computational Mechanics and Reliability at the University of Greenwich, London, United Kingdom. He received his PhD in Computational Modelling from Thames Polytechnic in 1988, and an MBA in Technology Management from the Open University in 1996. Before joining Greenwich in 1991, he worked for three years at Carnegie Mellon University (USA) as a research fellow in materials engineering. His research has resulted in over 250 publications. He is currently an Associate Editor for the CPMT Transactions and has been a guest editor on the journal of Soldering and Surface Mount Technology. In 2008 he was the General Chair for the IEEE ESTC conference in London and is a regular attendee and committee member of CPMT conferences such as ECTC and EPTC as well as conferences such as Eurosime (Europe), ICEPT (China), and IMPACT (Taiwan). In 2014 he organised the Therminic Conference in Greenwich, London. His research interests are related computational methods for design of engineering components and systems. Chris is a Senior Member of IEEE, Member of IET and is current Vice-President for conferences for IEEE-CPMT society.

## **ESREF 2015 Tutorials**

Within the frame of ESREF 2015, we offer a series of attractive tutorials on important issues of electronics. Since avionic and aeronautic applications are in focus of this year's conference, related tutorials deal with reliability and power electronics as well as PCB- and system-related analysis and anamnesis approaches towards root cause finding. Take the opportunity looking beyond the scope of device-related failure analysis by learning from experienced tutorialists from industry and research. In order to allow tutorial access independent from competing parallel sessions, the tutorials are embedded as plenary sessions within the regular program. We look forward to welcoming you there.

#### Tuesday October 6 - 8:20, Guillaumet room

#### **Tutorial Session E1: Packages & Assembly**

#### T1. Minimizing Defects by Design for Soldering

#### Thomas AHRENS, TrainAlytics GmbH, Germany

Soldering is by far the most used joining technology for electronic assemblies on printed circuit boards. With small pitch, lead-free soldering and hidden solder joints there are strong challenges and process issues to keep solder defect rates low. Observing certain design rules helps a lot. This tutorial presents key points in geometry of solder lands, material and process tolerances, paste volume vs. solder fillet volume, and needs for process control. You will learn how to classify and count solder defects and be able to sort them according to possible origin. In many cases there are checklists available from various IPC standards, which give a base or a starting point for an appropriate technological approach. Target groups for this tutorial are designers, process and quality specialists and managers. It provides design for manufacturing procedures to enhance the productivity of electronic assemblies, thus reducing the probability of solder defects.

**Dr. Thomas Ahrens** is active as consultant in the field of quality and reliability, production and repair of electronic assemblies. On a background of materials sciences, he has over 25 years of reputation in trouble shooting and qualification of materials, processes and personnel. His work methods include customized on-site investigation, mediation of seminars, workshops and practical training for industry clients. Dr. Ahrens collects his experiences from a rich fund of public research and development projects, and quality and damage analysis cases. Dr. Ahrens is Master Trainer for IPC-A-610 and J-STD-001 and chairs the DVS thematic group FG 4.11 Education in Solder Process for Electronic Assemblies. Dr. Ahrens is Managing Partner of Trainalytics GmbH, DE-Lippstadt, a company serving electronics industry in employees training,

product quality and physical defect analysis.

#### Tuesday October 6 - 9:20, Argos room Tutorial Session E2: MEMS, MOEMS, NEMS & Nano-objects

#### T2. MEMS Failure modes, FA and reliability challenges

#### Jérémie DHENNIN, Elemca, France

Challenges in the successful industrialization of MEMS devices are probably now related to their reliability. When lifetime is a first order criterion, reliability should be addressed since the early stages of development. The purpose of the tutorial will be to introduce the methodologies to evaluate the reliability of MEMS devices, as well as the conventional or custom techniques that can be used for that purpose. Indeed, the standard approaches for reliability assessment or qualification of microelectronics devices are insufficient to account for the MEMS peculiarities (multi-physical effects). A case study on RF-MEMS devices will be presented during the tutorial.

**Jeremie Dhennin** received his master degree in Micro and Nano Physics from the university of Paul Sabatier in Toulouse, France in 2005. He joined NOVAMEMS as a research engineer working on multi-physical characterization and modeling of MEMS switches failure mechanisms. His research activities focused on RF MEMS switches reliability, failure analysis and modeling, especially dealing with micro-contact issues. Since 2012, his technical scope has evolved to more generic reliability issues, dealing with other types of MEMS or electronic components. His managerial experience and broad technical scope has allowed him to take the CEO position at FIALAB – now ELEMCA – at the beginning of 2013.

Tuesday October 6 - 14:20, Guillaumet room

#### **Tutorial Session E1: Packages & Assembly**

## T3. Avoiding Flex Cracks in Ceramic Capacitors (CerCaps): Analytical Tool for a Reliable Failure Analysis and Guidance for Positioning CerCaps on PCBs

#### Gert VOGEL, SIEMENS AG (Germany)

In every electronic assembly line where ceramic capacitors are used and printed circuit boards are depaneled the quality risk "flex cracks" is known. Unfortunately flex cracks in ceramic capacitors (cercaps) always extend under the metal terminations of the capacitors and electrical tests do only reveal about one percent of the affected parts. With a new method – etch away the terminations and look at the otherwise hidden cracks – it is possible to identify all sources of mechanical bending and warping. In the course of failure analysis is it helpful to know that most times not only the failed ceramic capacitor shows a crack pattern but also all the surrounding cercaps as well. Well-founded knowledge about different crack patterns

and failure modes also allows recognizing unsafe bending and warping lines on the PCB. This gives us a guidance to place the ceramic capacitors in optimal orientation not only to de-paneling lines but also in the vicinity of mounting and screw openings. Finally the different kinds of cercaps with internal layouts that prevent boards from failing even if flex cracks should show up are reviewed.

Dr. **Gert Vogel** has been with Siemens more than 30 years. Seven years he has been a semiconductor technologist in the Siemens DRAM production in Munich and Regensburg. Then he moved to Siemens Amberg where amongst other topics he is a specialist for failure analysis of electronic components.

#### Tuesday October 6 - 16:40, Cassiopee room

#### **Tutorial session G: Space, Aeronautic and Embedded Systems**

#### T4. Radiation effects on components at space level

#### Robert ECOFFET, CNES, France

The space radiation environment is a major constraint in satellite design and a source of many in-flight anomalies. In this communication, we will start with a brief overview of the space radiation environment. Then we will review the state of the art of major effects of radiation on electronic components, as taken into account in space projects today. This part of the talk will be illustrated by examples of radiation-induced spacecraft anomalies. In a third part, we will try to appreciate the possible new challenges brought by technology downscaling and the introduction of new materials and concepts. Finally, we will describe the "radiation hardness assurance" in space projects and highlight the steps where improvements and margin optimization could be made in this engineering process.

**Robert Ecoffet** was born in Marseille, France, on July 22, 1963. He graduated in 1987 with an engineer degree from the Ecole Supérieure d'Electricité, Gif sur Yvette, France, with a specialization in electronic properties of materials. After serving in the French Marine for his National duties, he joined as an engineer the French Space

Agency CNES (Centre National d'Etudes Spatiales). Since 25 years, he has been working for CNES in the field of space environment and radiation effects. He participated extensively in radiation testing and project support in this field, leaded many radiation effects and space environment modeling research activities, was responsible for the development of space environment and technological experiments, and was part of many spacecraft anomalies investigation teams. He co-authored more than 100 papers mainly published in the IEEE Transactions on Nuclear Sciences. He is a member of the RADECS Association (Radiation Effects on Electronic Components and Systems) steering board, and had the honor to serve as General Chairman of the 2014 IEEE Nuclear and Space Radiation Effects Conference. His position in CNES is senior expert in space environment and radiation effects, and responsible for CNES "space environment" R&D axis.

#### Tuesday October 6 - 17:20, Cassiopee room

#### **Tutorial session G: Space, Aeronautic and Embedded Systems**

#### **T5: Radiation and COTS at ground level**

#### Jean-Luc AUTRAN, Daniela MUNTEANU, Aix-Marseille University, CNRS, IM2NP, France

This tutorial will survey single event effects (SEE) induced by terrestrial cosmic rays on current commercial CMOS technologies. After describing the natural radiation environment at ground and atmospheric levels, the tutorial will describe the physics of SEEs, from the main mechanisms of interaction between atmospheric radiation (neutrons, protons, muons) and circuit materials to the electrical response of

transistors, cells and complete circuits. SEE characterization using accelerated and real-time tests will be examined, as well as modeling and numerical simulation issues. Special emphasis will finally concern the radiation response of advanced technologies, including deca-nanometer bulk, FD-SOI and FinFET families.

**Jean-Luc Autran** is distinguished professor of physics and electrical engineering at Aix-Marseille University and honorary member of the University Institute of France (IUF). He is also deputy director of the Institute for Materials, Microelectronics, and Nanosciences of Provence (IM2NP, UMR CNRS 7334) and the principal investigator of the Altitude Single-event effects Test European Platform (ASTEP). His current research interests focus on the physics of soft errors, from the characterization of natural radiation to Monte Carlo radiation

transport simulation. He is the author or coauthor of more than 300 papers published in international journals and conferences, and has supervised 28 Ph.D theses.

Daniela Munteanu is director of research at the National Center for Scientific Research (CNRS). She is a

fellow researcher at the Institute for Materials, Microelectronics, and Nanoscience of Provence (IM2NP, UMR CNRS 7334) and has 15 years of experience in characterization, modeling, and simulation of semiconductor devices. Her current research interests include emerging complementary-metal-oxide-semiconductor (CMOS) devices, compact modeling, numerical simulation in the domains of nanoelectronics, and radiation effects on components and circuits. She is also the author or coauthor of more than 200 papers published in international journals and conferences, and has supervised 12 Ph.D theses.

Wednesday October 7 - 14:20, Spot room Tutorial session C: Failure Analysis

#### T6. FA (=Failure Analysis and Anamnesis) and reliability at system level

#### Peter JACOB, EMPA Duebendorf, Switzerland

Most failure analysts are used to do failure analysis on device level but they hardly know about failure analysis and anamnesis on system level. Many device failure analysis wrap up with EOS, which in most cases also means "end of story". However, looking at root cause findings, a majority of device failures result from circuitry transients, environmental conditions or from passive component failures, which produce shorts or lose their protection function. The tutorial shows up systematic approaches on failure anamnesis, which ideally guides towards the failure root cause by a careful application evaluation. Numerous examples illustrate the methodology. In this context, classical device analysis becomes just a supporting function of the anamnesis, which includes statistical and physical failure occurrence, reliability aspects, reverse FMEA and fact sheet analysis. The goal of the tutorial is to open the device-minded view of failure analysts towards the operational environment, mission profiles and system-related physics-of-failure.

After studying Technical Physics in Munich, **Peter Jacob** started his professional work in 1981 as a failure analysis expert in IBM semiconductor plant Boeblingen until 1992. After a short period at Hitachi Scientific Instruments, where he was responsible for electron microscopy configurations and customer trainings, he joined ETH Zurich/ Empa as a senior expert for failure analysis on micro- and power-electronics from device to system level. In parallel to this work, in 1995 he joined to Swatch Group – EM Microelectronic Marin as a principal F/A engineer. Jacob has authored more than 60 contributed and invited papers including an ESREF Best Paper. He volunteers in the German ESD Forum, EDFAS and EuFANet. In 2007 he was appointed to a Honorary Professor of Technical University Munich and in 2010 he received the International Barkhausen Award of Technical University Dresden.

#### Wednesday October 7 - 16:40, Guillaumet room

#### **Tutorial session F: Power Devices**

#### T7. Mission profile and reliability on power electronics

## **Prof. Ke Ma and Prof. Huai WANG**, Aalborg University / **Peter de PLACE RIMMEN**, Danfoss Power Electronics

In many mission-critical applications of energy conversions such as renewables, electricity transmission, electric vehicles, and aircrafts, etc, the power electronics should be extremely reliable and robust to avoid high cost of failures. In order to meet this challenging requirement, there is an ongoing paradigm shift in this field from the statistics-based assessment to the physic-of-failures based analysis. In this shift the stress and strength models of the power electronics components need to be accurately built, and both of the factors are closely related to the operating conditions or mission profiles of the whole systems. These mission profiles will involve multi-disciplinary knowledge and new approaches for the design of reliability performances. In this tutorial an overview of the involved data for specifying reliability for a new product development will be first given, and the importance of mission profiles for the reliability R&D is emphasized from industry perspective. Afterwards a flow and structure, which can translate the mission profiles of applications to the reliability metrics of power electronics, is proposed with practical examples. And some emerging challenges and requirements for the reliability testing/validation are also addressed. Finally the potential methodologies and technology trends involved with mission profiles based reliability analysis are also discussed.

**Ke Ma** is currently an Assistant Professor at Aalborg University with the Center of Reliable Power Electronics (CORPE), where he is the leader of working package 4 involving reliability modeling and design tools development. His research interests are power electronics technology including reliability in the applications of power generation and consumption systems. In the last 4 years he has contributed more than 50 journal and conference papers including 4 book chapters in the field of power electronics and reliability. He is one of the lecturers for an Industrial/PhD course on "Reliability in Power Electronic Systems" at Aalborg University, and was invited as speaker at two of the European Center for Power Electronics (ECPE) workshops. Dr. Ma received the B.Eng. and M.Sc. degrees from Zhejiang

University, China and PhD degree from Aalborg University, Denmark. He was the receiver of the Excellent Young Wind Doctor Award 2014 by European Academy of Wind Energy, as well as a few IEEE prized paper awards. He is now serving as Associate Editor of IEEE Transactions on Industry Applications.

**Huai Wang** is currently an Assistant Professor with the Center of Reliable Power Electronics (CORPE) in the Department of Energy Technology, Aalborg University, Denmark. His current research interests include the reliability of power electronic systems and reliability of capacitors in power converters. He was one of the lecturers for a PhD course on Reliability in Power Electronic Systems at Aalborg University and was an invited speaker at the ECPE workshop on lifetime modeling and simulation. He has contributed a number of journal papers, including several concept papers on the design for reliability of power electronic systems. Dr. Wang received his PhD degree from the City University of Hong Kong, Hong Kong, in 2012. He is a Visiting Scientist with the ETH Zurich, Zurich, Switzerland, from August to September 2014 and with the Massachusetts Institute of Technology (MIT), Cambridge, MA, USA, from September to November 2013. He was with the

ABB Corporate Research Center, Baden, Switzerland, in 2009. He serves as an Associate Editor of IEEE Transactions on Power Electronics, and a Guest Associate Editor of two special issues on topics relevant

to reliability in power electronics.